单周期CPU设计(本次内容,将在上课时随机提问)

PPT第5章 第2部分预习题目

一、 预习内容及相关问题

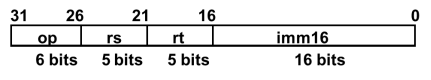

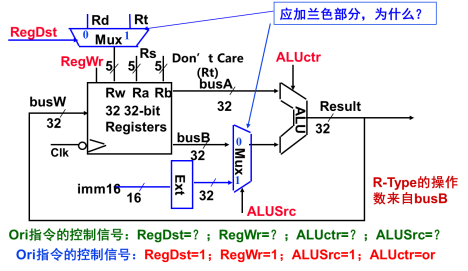

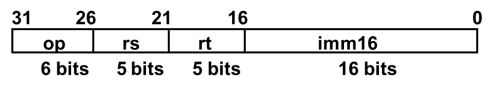

(一) 什么是R,I,J型指令,它们的特点?

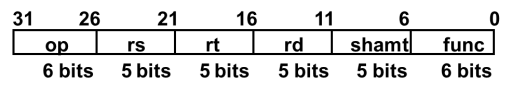

(二)R型指令的数据通路 (指令功能与其对应的逻辑结构)

功能:R[rd] ← R[rs] op R[rt],如:add rd, rs, rt

第2版图5.15(第3版图5.9)

- 第2版图5.15(第3版图5.9) R型指令的数据通路中busA ,busB的数据来自哪里?与Rt,Rs 有何联系?

- 第2版图5.15(第3版图5.9)中 通用寄存器有多少个?

- 写寄存器的控制信号是?如何选择所要写如的寄存器?结果通过那条传输线写回寄存器

- R型指令对ALU有几种操作?

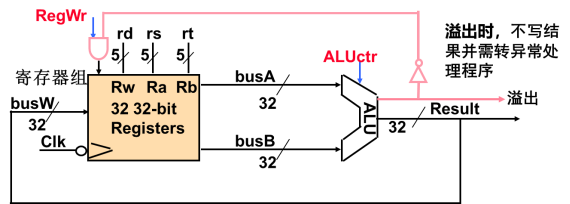

(三)I型指令的数据通路(指令功能与其对应的逻辑结构)

1. I型指令:I型立即数运算指令的数据通路

![]()

1)书中的表5.2中的11条指令中,有哪几条指令是I型指令立即数运算指令?源操作数寄存器如何确定?目标寄存器?

2)第2版 图5.16(第3版图5.10) I型指令立即数运算指令取指后,Rt选择的寄存器内容输出到busA? busB? 对结果有影响吗?

3)第2版 图5.16(第3版图5.10) 相对于图第2版5.15(图5.9)增加哪几部分?需要增加的控制信号及其作用?

4)第2版图5.16(第3版图5.10) I型指令立即数运算指令涉及对ALU有几种操作?

2 I型指令:Load/Store 指令的数据通路

![]()

1) Load指令的功能是什么?

2) Store指令的功能是什么?

3) 对照第2版图5.17(第3版图5.11),在第2版图5.16(第3版图5.10)数据通路上基础上,加哪些元件和连线?用何控制信号?

4) 这两类指令中的16位的带符号立即数进行符号扩展为32位,怎么扩展?

5) 第2版图5.17(第3版图5.11) Load/Store指令涉及对ALU有几种操作?

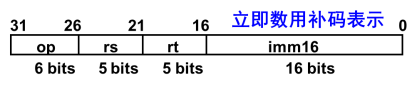

3.分支指令的数据通路

beq rs, rt, imm16

1)分支指令的功能?

2)判断的条件是什么?用到ALU有几种操作? 用到标志位?标志位怎么用?

3) 第2版图5.18(第3版图5.12) 比第2版图5.17(第3版图5.11) 增加了哪些单元?增加了哪些控制信号?

4)第2版图5.18(第3版图5.12)中两处出现了imm16,它们的作用一样吗?

5)解释图第2版5.19(第3版图5.13)工作原理。

(四)J型指令的数据通路 (指令功能与其对应的逻辑结构)

1)J指令的取指数据通路在第2版图5.20(第3版图5.14)中吗?若,没有,请指出是在哪个图中?

2)第2版图5.20(第3版图5.14)比第2版图5.19(第3版图5.13)增加了什么单元和控制信号?

3)第2版图5.20(第3版图5.14)的设计,新的PC值能否影响旧值,而影响当前指令执行?

(五)ALU的数据通路设计

根据指令集中R,I,J指令数据通路中用到的ALU操作进行详细设计。

1) R,I,J指令数据通路中共用几种ALU操作?可以用几位表示这些操作?

2) 第2版图5.13(第3版图5.7) ALuctr 是几位?如何得到的?

3) 第2版图5.13 (第3版图5.7)中3个MUX起什么作用?

4) ALU的加减控制信号是哪一个?

5) ALU标志位如何使用?

(六)控制逻辑单元设计

根据第2版图5.22(第3版 图5.16)完整的数据通路,分析控制信号取值。分析方法可参考PPT的第5章第一部分的第2,3节,第2版教材162-169(第3版 143-150)

因为取指阶段每一条指令都相同,故分析R,I,J各指令执行阶段。

1 分析每一条指令正确执行阶段的数据通路时,所有控制信号的取值,并进行列表,与表5.4对照

func op 控制信号 | 100000 | 100010 | 100011 | 101010 | 101011 | 与func无关 | |||||

000000 | 000000 | 000000 | 000000 | 000000 | 001101 | 001001 | 100011 | 101011 | 000100 | 000010 | |

R-add | R-sub | R-subu | R-slt | R-stlu | I-ori | I-addiu | I-lw | I-sw | I-beq | J-jump | |

Branch |

|

|

|

|

|

|

|

|

|

|

|

Jump |

|

|

|

|

|

|

|

|

|

|

|

RegDst |

|

|

|

|

|

|

|

|

|

|

|

ALUsrc |

|

|

|

|

|

|

|

|

|

|

|

ALUctr |

|

|

|

|

|

|

|

|

|

|

|

MemtoReg |

|

|

|

|

|

|

|

|

|

|

|

RegWr |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

ExtOp |

|

|

|

|

|

|

|

|

|

|

|

2 理解分层(多层)译码思想,教材P.166;参考本校教学平台本课程“教学资源”中第5章“计算机组成与设计:硬件 软件接口(第3版-中文.pdf,p195-197),在此基础上,分析表5.5,ALUop如何设计?

3.以上根据1,2内容,填写主控单元真值表:

| 000000 | 001101 | 001001 | 100011 | 101011 | 000100 | 000010 |

R型 | I-ori | I-addiu | I-lw | I-sw | I-beq | J-jump | |

Branch |

|

|

|

|

|

|

|

Jump |

|

|

|

|

|

|

|

RegDst |

|

|

|

|

|

|

|

ALUsrc |

|

|

|

|

|

|

|

ALUctr |

|

|

|

|

|

|

|

MemtoReg |

|

|

|

|

|

|

|

RegWr |

|

|

|

|

|

|

|

MemWr |

|

|

|

|

|

|

|

ExtOp |

|

|

|

|

|

|

|

ALUOP<2> |

|

|

|

|

|

|

|

ALUOP<1> |

|

|

|

|

|

|

|

ALUOP<0> |

|

|

|

|

|

|

|

R-tpye |

|

|

|

|

|

|

|

2 控制单元设计

1) 主控制器控制信号产生,请按照表5.4,表5.5写出控制信号表达式

Branch=

RegWr

ALUOP<2>=

ALUOP<1>=

ALUOP<0>=

R-type=

2) R型指令的涉及ALU控制信号的生成,即ALUctr<2:0>,如表5.6所示,写出控制信号表达式

ALUctr<2>=

ALUctr<1>=

ALUctr<0>=

二、参考资源

1 教学视频(袁春风老师,爱课程官网)

https://www.icourses.cn/sCourse/course_5884.html

2. 本校教学平台本课程“教学资源”中袁春风老师课件第5章“单周期CPU设计”

3. 本校教学平台本课程“教学资源”中第5章“计算机组成与设计:硬件 软件接口(第3版-中文.pdf,计算机组成与设计:硬件 软件接口(第3版,英文).pdf”