实验1、运算器组成实验

一、实验目的

(1)掌握算术逻辑运算加、减、乘、与的工作原理。

(2)熟悉简单运算器的数据传送通路。

(3)验证实验台运算器的8位加、减、与、直通功能。

(4)验证实验台的4位乘4位功能。

(5)按给定数据,完成几种指定的算术和逻辑运算。

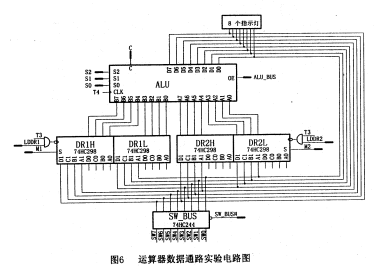

二、实验电路

图6示出了本实验所用的运算器数据通路图(接在运算器和存储器部分所标出接线孔上)。ALU由l片ISPLSIl024构成。四片4位的二选一输入寄存器74HC298构成两个操作数寄存器DRl和DR2,保存参与运算的数据。DRl接ALU的B数据输入端口,DR2接ALU的A数据输入端口,ALU的输出在ISPLSIl024内通过三态门发送到数据总线DBUS7-DBUS0上,进位信号C保存在ISPLSI1024内的一个D寄存器中。当实验台下部的IR/DBUS开关拨到DBUS位置时,8个红色发光二极管指示灯接在数据总线DBUS上,可显示运算结果或输入数据。另有一个指示灯C显示运算器进位信号状态。由ISPLSIl024构成的8位运算器的运算类型由选择端S2、S1、S0选择,功能表如下。

表3运算器运算类型选择表

选择 | 操作 | ||

S2 | S1 | S0 | |

0 | 0 | 0 | A&B |

0 | 0 | 1 | A&A |

0 | 1 | 0 | A+B |

0 | 1 | 1 | A-B |

1 | 0 | 0 | A( 低 4 位)*B(低 4 位) |

进位C只在加法运算和减法运算时产生,与、乘、直通操作不影响进位C的状态,即进位C保持不变。减法运算采用加减数的反码再加以1实现。在加法运算中,C代表进位:在减法运算中,C代表借位。运算产生的进位在T4的上升沿送入ISPLSI1024内的C寄存器保存。

在SW_BUS#信号为0时(SW_BUS# 表示低电平有效),参与运算的数据通过一个三态门74HC244(SW_BUS#)送到DBUS总线上,进而送至DR1或DR2操作数寄存器。输入数据可由实验台上的8个二进制数据开关SW7-SW0来设置,其中SW0是最低位,SW7是最高位。开关向上时为l,开关向下时为0。

图中尾巴上带粗短线标识的信号都是控制信号,控制信号均为电位信号。T3、T4是脉冲信号,印制板上已连接到实验台的时序电路产生的T3、T4信号上,实验中不用连线。S2、Sl、S0、ALU_BUS、LDDR2、LDDRl、Ml、M2、SW_BUS#各电位控制信号用电平开关K0-K15来模拟,若使用仿真系统,则需要仿真面板的连接与设置要求完成。K0-K15是一组用于模拟各控制电平信号的开关,开关向上时为l,开关向下时为0,每个开关无固定用途,可根据实验具体情况选用。S2、Sl、S0、ALU_BUS、LDDR2、LDDRl为高电平有效,SW_BUS#为低电平有效。M1=l时(高电平时),DRl选择Dl-Al作为数据输入端;M1=0时,DRl选择D0-A0作为数据输入端。当LDDRl=1时,在T3的下降沿,选中的数据被打入DRl寄存器。M2=1时,DR2选择D1-Al。作为数据输入端; M2=0时,DR2选择D0-A0作为数据输入端。当LDDR2=1时,在T3的下降沿,选中的数据被打入DR2寄存器。

数据总线DBUS有5个数据来源: 运算器ALU,寄存器堆RF控制台开关SW0-SW7,双端口存储器IDT7132和中断地址寄存器IAR。在任何时刻,都不允许2个或者2个以上的数据源同时向数据总线DBUS输送数据,只允许1个(或者没有)数据源向数据总线DBUS输送数据。在本实验中,为了保证数据的正确设置和观察,请令RS_BUS#=l, LRW=0,IAR_BUS#=1。

为了在实验中,每次只产生一组Tl、T2、T3、"T4脉冲,需将实验台上的DP、"DB、DZ开关进行正确设置。将DP开关置l,将DB、DZ开关置0,每按一次QD按钮,则顺序产生Tl、T2、T3、T4各一个单脉冲。本实验中采用单脉冲输出。

三、实验设备

(l)TEC 4A计算机组成原理实验系统1台

(2))直流万用表一只(也可以不用)

四、实验内容

(1)按图6或者仿真操作界面所示,正确连接运算器模块与实验台上的电平开关K0-K15。由于运算器的C和C指示灯、8位数据开关SW0-SW7、T3、T4的连线已由印制电路板连好,故接线任务仅仅是完成有关控制信号与电平开关K0-K15的连线,仿真系统参照仿真环境的连线与设置要求。在实验室的实验箱正确需要设置开关DZ、DB、DP。用数据开关SW7-SW0向DRl和DR2寄存器置数。请从“在线教育综合平台”本课程实验中下载本次实验的excel表格,在实验过程中将拨动开关与被控制信号对应连接关系和操作步骤、信号变化记录下来。

1. 置ALU_BUS=0,关闭ALU向数据总线DBUS的输出;置SW_ BUS#=0,开启数据开关SW7-SW0向数据总线DBUS的输出。注意,对于数据总线DBUS(或者其他任何总线),在任一时刻,只能有一个数据源向它输出。置IR/DBUS开关于DBUS位置,在数据开关SW7-SW0上设置各种数据,观察数据指示灯状态是否与数据开关状态一致。

2. 置M1=1,选择DBUS作为DRl的数据源;置LDDRl=l,按QD按钮,则将DBUS的数据打入DRl。置M2=1,选择DBUS作为DR2的数据源;置LDDR2=1,按QD按钮,则将DBUS的数据打入DR2。向DRl存入01010101,向DR2存入10101010。

3.置SW_BUS#=1,关闭数据开关SW7-SW0对数据总线DBUS的输出;置ALU_BUS=l,开启ALU对DBUS的输出。选择S2=0、S1=0、S0=1,便运算器进行直通运算,通过DBUS指示灯验证DR2中的内容是否为第2步设置的值。令S2=0、S1=1、S0=0,使运算器进行加运算,通过DBUS指示灯验证DR1中的内容是否为第2步设置的值。令S2=0、S1=1、S0=1,使运算器进行减法运算,通过DBUS指示灯验证结果。在表4中填入控制信号状态与DBUS显示状态。

表4 DRl、DR2设置值检查

ALU_BUS | SW_BUS# | 寄存器内容 | S2 S1 S0 | DBUS |

|

| DR1=01010101 DR2=10101010 |

|

|

|

| DR1=01010101 DR2=10101010 |

|

|

|

| DR1=01010101 DR2=10101010 |

|

|

(2)验证运算器的算术运算和逻辑运算功能。

令DRl=01010101B,DR2=10101010B,正确选择S2、S1、S0,依次进行与、乘法实验,记下实验结果(数据和进位)并对结果进行分析。

(3)在不外接电路的情况下(不修改任何连线),将A、B中的内容互换。(若DRl=01100011B,DR2=10110100B则交换后为DRl=10110100;DR2=01100011B)

(3)在不外接电路的情况下(不修改任何连线),将A、B中的内容互换。(若DRl=01100011B,DR2=10110100B则交换后为DRl=10110100;DR2=01100011B)

1